### Machine Minimization

ECE 152A - Summer 2009

### Reading Assignment

- Brown and Vranesic

- 8 Synchronous Sequential Circuits

- 8.6 State Minimization

- □ 8.6.1 Partitioning Minimization Procedure

- 8.6.2 Incompletely Specified FSMs

August 19, 2009

ECE 152A - Digital Design Principles

### Reading Assignment

#### ■ Roth

- 15 Reduction of State Tables / State Assignment

- 15.1 Elimination of Redundant States

- 15.2 Equivalent States

- 15.3 Determination of State Equivalence Using an Implication Table

- 15.4 Equivalent Sequential Circuits

- 15.5 Incompletely Specified State Tables

August 19, 2009

ECE 152A - Digital Design Principles

3

#### Elimination of Redundant States

- Row Matching

- Recall CD player controller

- Mealy implementation contained two sets of rows with same next state and output

- Eliminate redundant states

- Row matching doesn't identify "equivalent states"

- □ Row matching identifies "same state"

- Equivalent states are the more general case

August 19, 2009

ECE 152A - Digital Design Principles

### Equivalent States

- Definitions of equivalent states

- □ Roth: 2 states equivalent iff for every single input *x*, outputs are the same and next states are equivalent (as opposed to row matching)

- Pairwise comparison using implication table

- □ Kohavi : Iff for every possible input sequence the same output sequence will be produced regardless of whether S<sub>i</sub> or S<sub>i</sub> is the initial state

- Moore reduction procedure to find equivalence partition

August 19, 2009

ECE 152A - Digital Design Principles

5

# Determination of State Equivalence using an Implication Table

#### ■ Find Equivalent Pairs

|   | INS |            |   |     |  |

|---|-----|------------|---|-----|--|

|   | PS  | PS x=0 x=1 |   |     |  |

| А |     | D          | С | 0   |  |

|   | В   | F          | Н | 0   |  |

|   | С   | E          | D | 1   |  |

|   | D   | Α          | Е | 0   |  |

|   | E   | С          | Α | 1   |  |

|   | F   | F          | В | 1   |  |

|   | G   | В          | Н | 0   |  |

|   |     | l .        |   | l . |  |

August 19, 2009

ECE 152A - Digital Design Principles

С

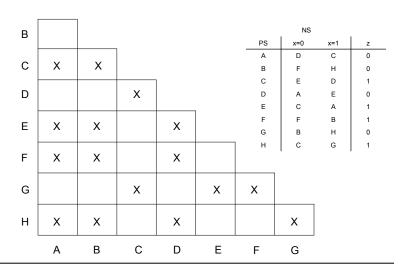

- (1) Construct Implication Table for Pairwise Comparison

- (2) First Pass

- Compare outputs

- For states to be equivalent, next state and output must be the same

- Put "X's" where outputs differ

August 19, 2009

ECE 152A - Digital Design Principles

7

### Implication Table (first pass)

August 19, 2009

ECE 152A - Digital Design Principles

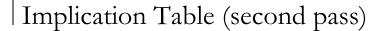

(3) One column (or row) at a time, find implied pairs

August 19, 2009

ECE 152A - Digital Design Principles

August 19, 2009

ECE 152A - Digital Design Principles

- (3) One column (or row) at a time, find implied pairs (cont)

- Remove self implied pairs

- A-D in cell A-D

- C-E in cell C-E

- Remove same state pairs

- H-H in cell B-G

- C-C in cell H-E

August 19, 2009

ECE 152A - Digital Design Principles

11

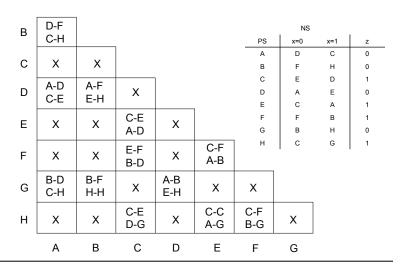

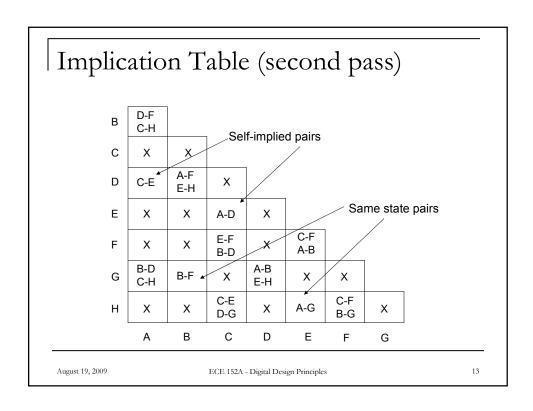

#### Implication Table (second pass) D-F В C-H Self-implied pairs С Х A-D4 A-F D Χ C-E E-H C-E Same state pairs Ε Χ Χ Χ A-D C-F E-F Χ Χ A-B B-D B-D A-B Χ Χ G Χ Н-Н E-H C-E C-C C-F Н Χ Χ Χ Χ D-G A-G B-G Α С G В D Ε F August 19, 2009 12 ECE 152A - Digital Design Principles

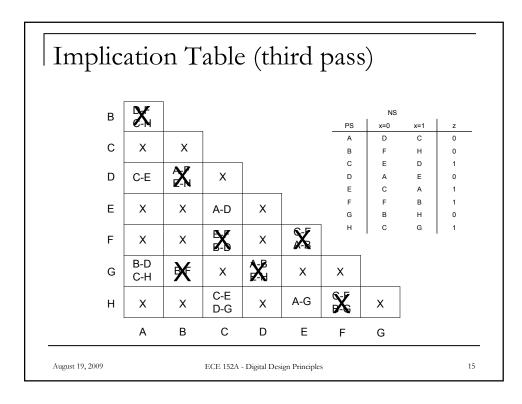

(4) One column (or row) at a time, eliminate implied pairs

August 19, 2009

ECE 152A - Digital Design Principles

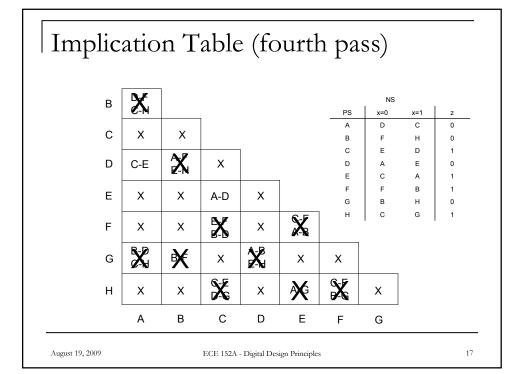

- (5) Next pass, one column (or row) at a time, eliminate implied pairs

- (6) Continue until pass results in no further elimination of implied pairs

August 19, 2009

ECE 152A - Digital Design Principles

- (7) Combine equivalent states (based on coordinates of cells, not contents)

- □  $A \equiv D, C \equiv E \text{ in example}$

- Equivalence is pairwise

□ A ≡ B, B ≡ C implies A ≡ C (transitive)

- (8) Construct reduced state table

August 19, 2009

ECE 152A - Digital Design Principles

#### ■ Reduced State Table

□ \* indicates change from original state table

| NS          |              |              |   |  |  |  |

|-------------|--------------|--------------|---|--|--|--|

| PS          | PS x=0 x=1   |              |   |  |  |  |

| Α           | A*           | С            | 0 |  |  |  |

| В           | F            | Н            | 0 |  |  |  |

| С           | C*           | A*           | 1 |  |  |  |

| F           | F            | В            | 1 |  |  |  |

| G           | В            | Н            | 0 |  |  |  |

| Н           | С            | G            | 1 |  |  |  |

| C<br>F<br>G | C*<br>F<br>B | A*<br>B<br>H | 1 |  |  |  |

August 19, 2009

ECE 152A - Digital Design Principles

19

# Determination of State Equivalence using an Implication Table

- Row Matching on an Implication Table

- Mealy Machine outputs

- Recall 101 sequence detector (direct Mealy conversion)

| NS,z |                   |  |  |  |  |

|------|-------------------|--|--|--|--|

| x=0  | x=1               |  |  |  |  |

| A,0  | B,0               |  |  |  |  |

| C,0  | B,0               |  |  |  |  |

| A,0  | D,1               |  |  |  |  |

| C,0  | B,0               |  |  |  |  |

|      | A,0<br>C,0<br>A,0 |  |  |  |  |

August 19, 2009

ECE 152A - Digital Design Principles

### Implication Table

- Same state pairs

- Eliminate implied pairs

- Matching rows

- No implied pairs

- B and D are "same state"

| NS,z |     |     |  |  |  |

|------|-----|-----|--|--|--|

| PS   | x=0 | x=1 |  |  |  |

| Α    | A,0 | B,0 |  |  |  |

| В    | C,0 | B,0 |  |  |  |

| С    | A,0 | D,1 |  |  |  |

| D    | C,0 | B,0 |  |  |  |

August 19, 2009

ECE 152A - Digital Design Principles

21

#### Moore Reduction Procedure

■ States S<sub>i</sub> and S<sub>j</sub> of machine M are said to be equivalent If and only if, for every possible input sequence, the same output sequence will be produced regardless of whether S<sub>i</sub> or S<sub>i</sub> is the initial state

Zvi Kohavi, Switching and Finite Automata Theory

August 19, 2009

ECE 152A - Digital Design Principles

- Two states,  $S_i$  and  $S_j$ , of machine M are <u>distinguishable</u> if and only if there exists at least one finite input sequence which, when applied to M, causes different output sequences depending on whether  $S_i$  or  $S_j$  is the initial state

- □ The sequence which distinguishes these states is called a <u>distinguishing sequence of the pair (S<sub>i</sub>, S<sub>i</sub>)</u>

August 19, 2009

ECE 152A - Digital Design Principles

23

#### Moore Reduction Procedure

- If there exists for pair  $(S_i, S_j)$  a distinguishing sequence of length  $\underline{k}$ , the states in  $(S_i, S_j)$  are said to be  $\underline{k}$ -distinguishable

- States that are not k-distinguishable are said to be k-equivalent

August 19, 2009

ECE 152A - Digital Design Principles

- The result sought is a partition of the states of M such that two states are in the same block if and only if they are equivalent

- □ *P*<sub>0</sub> corresponds to 0-distinguishablity (includes all states of machine M)

- P<sub>1</sub> is obtained simply by inspecting the table and placing those states having the same outputs, under all inputs, in the same block

- P₁ establishes the sets of states which are 1-equivalent

August 19, 2009

ECE 152A - Digital Design Principles

25

#### Moore Reduction Procedure

- Obtain partition P<sub>2</sub>

- □ This step is carried out by splitting blocks of P<sub>1</sub>, whenever their successors are not contained in a common block of P<sub>1</sub>

- Iterate process of splitting blocks

- □ If for some k,  $P_{k+1} = P_k$ , the process terminates and  $P_k$  defines the sets of equivalent states of the machine

- □ P<sub>k</sub> is thus called the equivalence partition

- The equivalence partition is unique

August 19, 2009

ECE 152A - Digital Design Principles

Recall state table from earlier example

| NS |     |     |   |  |

|----|-----|-----|---|--|

| PS | x=0 | x=1 | z |  |

| Α  | D   | С   | 0 |  |

| В  | F   | Н   | 0 |  |

| С  | E   | D   | 1 |  |

| D  | Α   | Е   | 0 |  |

| Е  | С   | Α   | 1 |  |

| F  | F   | В   | 1 |  |

| G  | В   | Н   | 0 |  |

| Н  | С   | G   | 1 |  |

|    |     |     |   |  |

August 19, 2009

ECE 152A - Digital Design Principles

27

#### Moore Reduction Procedure

- $P_0$  = (ABCDEFGH)

- P<sub>1</sub> is obtained by splitting states having different outputs

- $P_1 = (ABDG)(CEFH)$

- Block 1 = ABDG, Block 2 = CEFH

| PS | x=0 | x=1 | z |

|----|-----|-----|---|

| Α  | D   | С   | 0 |

| В  | F   | Н   | 0 |

| С  | E   | D   | 1 |

| D  | Α   | E   | 0 |

| E  | С   | Α   | 1 |

| F  | F   | В   | 1 |

| G  | В   | Н   | 0 |

| Н  | С   | G   | 1 |

August 19, 2009

ECE 152A - Digital Design Principles

- Obtain P<sub>2</sub>

- □ Block 1 = ABDG, Block 2 = CEFH

August 19, 2009

ECE 152A - Digital Design Principles

2

#### Moore Reduction Procedure

- Obtain P<sub>2</sub> (cont)

- □ Block 1 = ABDG, Block 2 = CEFH

August 19, 2009

ECE 152A - Digital Design Principles

- Split B out of block 1

- □ B is "2 distinguishable" from A, D and G

- No states of block 2 are "2 distinguishable"

- P<sub>2</sub> = (ADG)(B)(CEFH)

- □ Block 1 = ADG

- □ Block 2 = B

- □ Block 3 = CEFH

August 19, 2009

ECE 152A - Digital Design Principles

31

#### Moore Reduction Procedure

■ Obtain P<sub>3</sub>

$$P_2 = (ADG)(B)(CEFH)$$

| Α | D | С | 0 |

|---|---|---|---|

| В | F | Н | 0 |

| С | E | D | 1 |

| D | Α | E | 0 |

| Ε | С | Α | 1 |

| F | F | В | 1 |

| G | В | Н | 0 |

| Н | С | G | 1 |

|   |   |   |   |

August 19, 2009

ECE 152A - Digital Design Principles

- Obtain P<sub>3</sub> (cont)

- □ Split G from block 1

- G is 3-distinguishable from A and D

- □ Split F from block 3

- F is 3-distinguishable from C, E and H

- $\blacksquare$  P<sub>3</sub> = (AD)(G)(B)(CEH)(F)

- □ Block 1 = AD, block 2 = G, block 3 = B, block 4 = CEH and block 5 = F

August 19, 2009

ECE 152A - Digital Design Principles

33

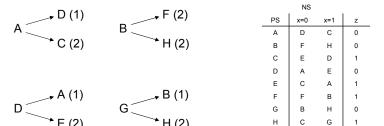

#### Moore Reduction Procedure

■ Obtain P₄

$$P_3 = (AD)(G)(B)(CEH)(F)$$

| . , , , , | , , , , |   |   | • | ľ |

|-----------|---------|---|---|---|---|

|           |         | В | F | Н | 0 |

|           |         | С | E | D | 1 |

|           |         | D | Α | E | 0 |

|           |         | E | С | Α | 1 |

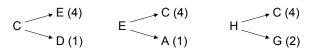

| → D (1)   | → A (1) | F | F | В | 1 |

| _         | D _     | G | В | Н | 0 |

| C (4)     | E (4)   | Н | С | G | 1 |

| ` '       | ` '     |   |   |   |   |

August 19, 2009

ECE 152A - Digital Design Principles

- Obtain P<sub>4</sub> (cont)

- □ Split H from block 4

- H is 4-distinguishable from C and E

- $P_4 = (AD)(G)(B)(CE)(H)(F)$

- □ Block 1 = AD, block 2 = G, block 3 = B, block 4 = CEH, block 5 = H and block 6 = F

August 19, 2009

ECE 152A - Digital Design Principles

35

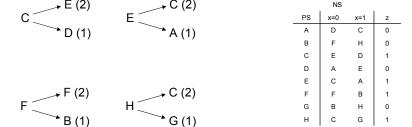

#### Moore Reduction Procedure

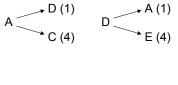

- Obtain P<sub>5</sub>

- $P_4 = (AD)(G)(B)(CE)(H)(F)$

| E (4)   | _ C (4) |

|---------|---------|

| C D (1) | E A (1) |

| NS |   |   |   |  |  |

|----|---|---|---|--|--|

| PS | z |   |   |  |  |

| Α  | D | С | 0 |  |  |

| В  | F | Н | 0 |  |  |

| C  | E | D | 1 |  |  |

| D  | Α | E | 0 |  |  |

| E  | С | Α | 1 |  |  |

| F  | F | В | 1 |  |  |

| G  | В | Н | 0 |  |  |

| Н  | С | G | 1 |  |  |

August 19, 2009

ECE 152A - Digital Design Principles

- Obtain P<sub>5</sub> (cont)

- No blocks split from P<sub>5</sub>

- $P_5 = P_4 = (AD)(G)(B)(CE)(H)(F)$

- $\square$  P<sub>5</sub> = P<sub>4</sub> = equivalence partition

- □ Same result as implication table

August 19, 2009

ECE 152A - Digital Design Principles

37

# Reduction of Incompletely Specified State Tables

Use "modified row matching" to combine states

|    | NS  |     | Z   |     |                                 |

|----|-----|-----|-----|-----|---------------------------------|

| PS | x=0 | x=1 | x=0 | x=1 |                                 |

| Α  | -   | В   | -   | -   | A and C can be combined         |

| В  | С   | D   | -   | -   | A and D can be combined         |

| С  | Α   | -   | 0   | -   |                                 |

| D  | Α   | -   | 1   | -   | C and D cannot (outputs differ) |

August 19, 2009

ECE 152A - Digital Design Principles

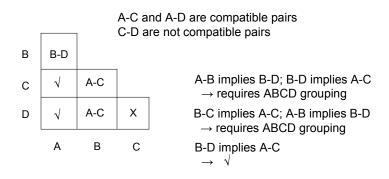

## Reduction of Incompletely Specified State Tables

- Using an Implication Table

- State pairs are compatible, not equivalent

- □ States must be "pairwise" compatible

- ABC requires A-B, B-C and A-C

- Compatible relationship is not transitive like equality

- Compatible pairs must be grouped and included in reduced machine

August 19, 2009

ECE 152A - Digital Design Principles

39

# Reduction of Incompletely Specified State Tables

lacksquare  $\sqrt{\ }$  indicates "compatible pair"

August 19, 2009

ECE 152A - Digital Design Principles

# Reduction of Incompletely Specified State Tables

- Heuristic (non-deterministic) process

- □ Requires "trial and error"

- Not necessarily minimal

|    | NS  |     | Z   |     |

|----|-----|-----|-----|-----|

| PS | x=0 | x=1 | x=0 | x=1 |

| AC | AC  | BD  | 0   | -   |

| BD | AC  | BD  | 1   | -   |

August 19, 2009

ECE 152A - Digital Design Principles